Démultiplexeur

Un démultiplexeur est un circuit combinatoire qui n'a qu'une seule ligne d'entrée et 2 N lignes de sortie. Simplement, le multiplexeur est un circuit combinatoire à entrée unique et à sorties multiples. Les informations sont reçues des lignes d'entrée uniques et dirigées vers la ligne de sortie. En fonction des valeurs des lignes de sélection, l'entrée sera connectée à l'une de ces sorties. Le démultiplexeur est opposé au multiplexeur.

Contrairement au codeur et au décodeur, il y a n lignes de sélection et 2 n les sorties. Il y a donc au total 2 n combinaisons possibles d’entrées. Le démultiplexeur est également traité comme Démultiplexage .

Il existe différents types de démultiplexeurs qui sont les suivants :

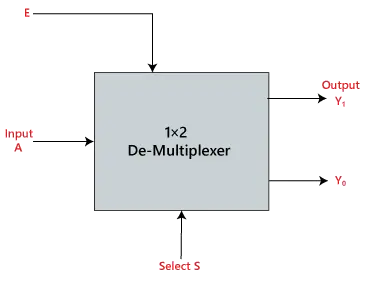

Démultiplexeur 1×2 :

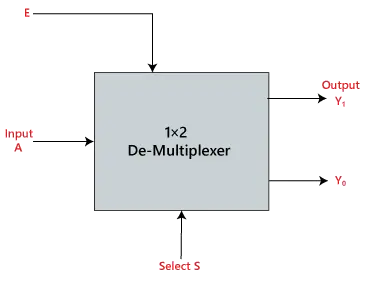

Dans le démultiplexeur 1 à 2, il n'y a que deux sorties, c'est-à-dire Y 0 , Andy 1 , 1 lignes de sélection, c'est-à-dire S 0 , et une entrée unique, c'est-à-dire A. Sur la base de la valeur de sélection, l'entrée sera connectée à l'une des sorties. Le schéma fonctionnel et la table de vérité du 1 × 2 multiplexeurs sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

ET 0 =S 0 '.UN

ET 1 =S 0 .UN

Le circuit logique des expressions ci-dessus est donné ci-dessous :

Démultiplexeur 1×4 :

Dans le démultiplexeur 1 à 4, il y a un total de quatre sorties, c'est-à-dire Y 0 , ET 1 , ET 2 , Andy 3 , 2 lignes de sélection, soit S 0 et S 1 et une entrée unique, c'est-à-dire A. Sur la base de la combinaison d'entrées présentes au niveau des lignes de sélection S 0 et S 1 , l'entrée soit connectée à l'une des sorties. Le schéma fonctionnel et la table de vérité du 1 × 4 multiplexeurs sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

ET 0 =S 1 'S 0 ' UN

et 1 =S 1 'S 0 UN

et 2 =S 1 S 0 ' UN

et 3 =S 1 S 0 UN

Le circuit logique des expressions ci-dessus est donné ci-dessous :

Démultiplexeur 1 × 8

Dans le démultiplexeur 1 à 8, il y a un total de huit sorties, c'est-à-dire Y 0 , ET 1 , ET 2 , ET 3 , ET 4 , ET 5 , ET 6 , Andy 7 , 3 lignes de sélection, soit S 0 , S 1 et S 2 et une entrée unique, c'est-à-dire A. Sur la base de la combinaison d'entrées présentes au niveau des lignes de sélection S 0 , S 1 et S 2 , l'entrée sera connectée à l'une de ces sorties. Le schéma fonctionnel et la table de vérité du 1 × 8 démultiplexeurs sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

ET 0 =S 0 '.S 1 '.S 2 '.UN

ET 1 =S 0 .S 1 '.S 2 '.UN

ET 2 =S 0 '.S 1 .S 2 '.UN

ET 3 =S 0 .S 1 .S 2 '.UN

ET 4 =S 0 '.S 1 '.S 2 UN

ET 5 =S 0 .S 1 '.S 2 UN

ET 6 =S 0 '.S 1 .S 2 UN

ET 7 =S 0 .S 1 .S 3 .UN

Le circuit logique des expressions ci-dessus est donné ci-dessous :

Démultiplexeur 1 × 8 utilisant un démultiplexeur 1 × 4 et 1 × 2

Nous pouvons mettre en œuvre le 1 × 8 démultiplexeur utilisant un démultiplexeur d'ordre inférieur. Pour mettre en œuvre le 1 × 8 démultiplexeur, il nous en faut deux 1 × 4 démultiplexeurs et un 1 × 2 démultiplexeurs. Le 1 × 4 multiplexeur dispose de 2 lignes de sélection, 4 sorties et 1 entrée. Le 1 × 2 démultiplexeurs n'ont qu'une seule ligne de sélection.

Pour obtenir 8 sorties de données, nous avons besoin de deux 1 × 4 démultiplexeurs. Le démultiplexeur 1 × 2 produit deux sorties. Ainsi, afin d'obtenir le résultat final, nous devons transmettre les sorties du démultiplexeur 1 × 2 comme entrée du 1 × 4 démultiplexeurs. Le schéma fonctionnel de 1 × 8 démultiplexeur utilisant 1 × 4 et 1 × 2 démultiplexeurs est donné ci-dessous.

1 x 16 démultiplexeur

Dans le démultiplexeur 1 × 16, il y a un total de 16 sorties, soit Y 0 , ET 1 , …, ET 16 , 4 lignes de sélection, soit S 0 , S 1 , S 2 , et S 3 et une entrée unique, c'est-à-dire A. Sur la base de la combinaison d'entrées présentes au niveau des lignes de sélection S 0 , S 1 , et S 2 , l'entrée sera connectée à l'une de ces sorties. Le schéma fonctionnel et la table de vérité du 1 × 16 démultiplexeurs sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

ET 0 =A.S 0 '.S 1 '.S 2 '.S 3 '

ET 1 =A.S 0 '.S 1 '.S 2 '.S 3

ET 2 =A.S 0 '.S 1 '.S 2 .S 3 '

ET 3 =A.S 0 '.S 1 '.S 2 .S 3

ET 4 =A.S 0 '.S 1 .S 2 '.S 3 '

ET 5 =A.S 0 '.S 1 .S 2 '.S 3

ET 6 =A.S 0 '.S 1 .S 2 .S 3 '

ET 7 =A.S 0 '.S 1 .S 2 .S 3

ET 8 =A.S 0 .S 1 '.S 2 '.S 3 '

ET 9 =A.S 0 .S 1 '.S 2 '.S 3

ET dix =A.S 0 .S 1 '.S 2 .S 3 '

ET onze =A.S 0 .S 1 '.S 2 .S 3

ET 12 =A.S 0 .S 1 .S 2 '.S 3 '

ET 13 =A.S 0 .S 1 .S 2 '.S 3

ET 14 =A.S 0 .S 1 .S 2 .S 3 '

ET quinze =A.S 0 .S 1 .S 2 '.S 3

Le circuit logique des expressions ci-dessus est donné ci-dessous :

Démultiplexeur 1 × 16 utilisant un démultiplexeur 1 × 8 et 1 × 2

Nous pouvons mettre en œuvre le 1 × 16 démultiplexeur utilisant un démultiplexeur d'ordre inférieur. Pour mettre en œuvre le 1 × 16 démultiplexeur, il nous en faut deux 1 × 8 démultiplexeurs et un 1 × 2 démultiplexeurs. Le 1 × Le multiplexeur 8 dispose de 3 lignes de sélection, 1 entrée et 8 sorties. Le 1 × 2 démultiplexeurs n'ont qu'une seule ligne de sélection.

Pour obtenir 16 sorties de données, nous avons besoin de deux démultiplexeurs 1 × 8. Le 1 × 8 démultiplexeurs produisent huit sorties. Donc, pour obtenir le résultat final, nous avons besoin d'un 1 × 2 démultiplexeurs pour produire deux sorties à partir d'une seule entrée. Ensuite, nous transmettons ces sorties au démultiplexeur en tant qu'entrée. Le schéma fonctionnel de 1 × 16 démultiplexeur utilisant 1 × 8 et 1 × 2 démultiplexeurs est donné ci-dessous.