Demultiplekser

Demultiplekser to obwód kombinacyjny, który ma tylko 1 linię wejściową i 2 N linie wyjściowe. Mówiąc najprościej, multiplekser jest obwodem kombinacyjnym z jednym wejściem i wieloma wyjściami. Informacja odbierana jest z pojedynczych linii wejściowych i kierowana na linię wyjściową. Na podstawie wartości linii wyboru wejście zostanie podłączone do jednego z tych wyjść. Demultiplekser jest przeciwieństwem multipleksera.

W przeciwieństwie do kodera i dekodera, istnieje n linii wyboru i 2 N wyjścia. Zatem w sumie jest 2 N możliwe kombinacje wejść. Demultiplekser jest również traktowany jako De-mux .

Istnieją różne typy demultiplekserów, które są następujące:

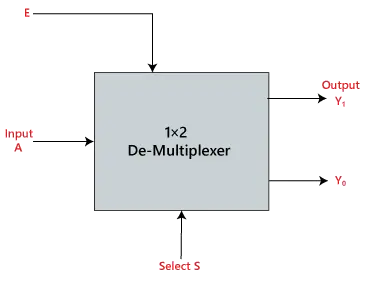

Demultiplekser 1×2:

W demultiplekserze 1 do 2 są tylko dwa wyjścia, tj. Y 0 i Y 1 , 1 linie wyboru, czyli S 0 , oraz wejście pojedyncze, czyli A. Na podstawie wybranej wartości wejście zostanie podłączone do jednego z wyjść. Schemat blokowy i tabela prawdy 1 × Poniżej podano 2 multipleksery.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

I 0 =S 0 '.A

I 1 =S 0 .A

Poniżej przedstawiono obwód logiczny powyższych wyrażeń:

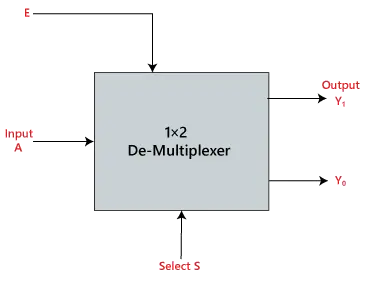

Demultiplekser 1×4:

W demultiplekserze 1 do 4 znajdują się w sumie cztery wyjścia, tj. Y 0 , I 1 , I 2 i Y 3 , 2 linie selekcji, tj. S 0 i S 1 i pojedynczego wejścia, tj. A. Na podstawie kombinacji wejść, które występują na liniach wyboru S 0 i S 1 , wejście należy podłączyć do jednego z wyjść. Schemat blokowy i tabela prawdy 1 × Poniżej podano 4 multipleksery.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

I 0 =S 1 ' S 0 ' A

I 1 =S 1 ' S 0 A

I 2 =S 1 S 0 ' A

I 3 =S 1 S 0 A

Poniżej przedstawiono obwód logiczny powyższych wyrażeń:

Demultiplekser 1×8

W demultiplekserze od 1 do 8 dostępnych jest łącznie osiem wyjść, tj. Y 0 , I 1 , I 2 , I 3 , I 4 , I 5 , I 6 i Y 7 , 3 linie selekcji, tj. S 0 , S 1 i S 2 i pojedynczego wejścia, tj. A. Na podstawie kombinacji wejść, które występują na liniach wyboru S 0 , S 1 i S 2 , wejście zostanie podłączone do jednego z tych wyjść. Schemat blokowy i tabela prawdy 1 × Poniżej podano 8 demultiplekserów.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

I 0 =S 0 '.S 1 '.S 2 '.A

I 1 =S 0 .S 1 '.S 2 '.A

I 2 =S 0 '.S 1 .S 2 '.A

I 3 =S 0 .S 1 .S 2 '.A

I 4 =S 0 '.S 1 '.S 2 A

I 5 =S 0 .S 1 '.S 2 A

I 6 =S 0 '.S 1 .S 2 A

I 7 =S 0 .S 1 .S 3 .A

Poniżej przedstawiono obwód logiczny powyższych wyrażeń:

Demultiplekser 1×8 wykorzystujący demultiplekser 1×4 i 1×2

Możemy wdrożyć 1 × 8 demultipleksera wykorzystującego demultiplekser niższego rzędu. Aby wdrożyć 1 × 8 demultipleksera, potrzebujemy dwóch 1 × 4 demultipleksery i jeden 1 × 2 demultipleksery. 1 × Multiplekser 4 ma 2 linie wyboru, 4 wyjścia i 1 wejście. 1 × 2 demultiplekser ma tylko 1 linię wyboru.

Aby uzyskać 8 wyjść danych, potrzebujemy dwóch 1 × 4 demultiplekser. Demultiplekser 1×2 generuje dwa wyjścia. Zatem, aby uzyskać końcowy wynik, musimy przekazać wyjścia demultipleksera 1×2 jako wejście obu × 4 demultiplekser. Schemat blokowy 1 × 8 demultipleksera przy użyciu 1 × 4 i 1 × 2 de-multiplekser podano poniżej.

Demultiplekser 1 x 16

W demultiplekserze 1×16 jest łącznie 16 wyjść, tj. Y 0 , I 1 , …, I 16 , 4 linie selekcji, tj. S 0 , S 1 , S 2 i S 3 i pojedynczego wejścia, tj. A. Na podstawie kombinacji wejść, które występują na liniach wyboru S 0 , S 1 i S 2 , wejście zostanie podłączone do jednego z tych wyjść. Schemat blokowy i tabela prawdy 1 × Poniżej podano 16 demultiplekserów.

Schemat blokowy:

Tabela prawdy:

Logiczne wyrażenie terminu Y jest następujące:

I 0 =AS 0 '.S 1 '.S 2 '.S 3 '

I 1 =AS 0 '.S 1 '.S 2 '.S 3

I 2 =AS 0 '.S 1 '.S 2 .S 3 '

I 3 =AS 0 '.S 1 '.S 2 .S 3

I 4 =AS 0 '.S 1 .S 2 '.S 3 '

I 5 =AS 0 '.S 1 .S 2 '.S 3

I 6 =AS 0 '.S 1 .S 2 .S 3 '

I 7 =AS 0 '.S 1 .S 2 .S 3

I 8 =AS 0 .S 1 '.S 2 '.S 3 '

I 9 =AS 0 .S 1 '.S 2 '.S 3

I 10 =AS 0 .S 1 '.S 2 .S 3 '

I jedenaście =AS 0 .S 1 '.S 2 .S 3

I 12 =AS 0 .S 1 .S 2 '.S 3 '

I 13 =AS 0 .S 1 .S 2 '.S 3

I 14 =AS 0 .S 1 .S 2 .S 3 '

I piętnaście =AS 0 .S 1 .S 2 '.S 3

Poniżej przedstawiono obwód logiczny powyższych wyrażeń:

Demultiplekser 1×16 wykorzystujący demultiplekser 1×8 i 1×2

Możemy wdrożyć 1 × 16 demultipleksera wykorzystującego demultiplekser niższego rzędu. Aby wdrożyć 1 × 16 demultipleksera, potrzebujemy dwóch 1 × 8 demultiplekserów i jeden 1 × 2 demultipleksery. 1 × Multiplekser 8 ma 3 linie wyboru, 1 wejście i 8 wyjść. 1 × 2 demultiplekser ma tylko 1 linię wyboru.

Aby uzyskać 16 wyjść danych, potrzebujemy dwóch demultiplekserów 1×8. 1 × Demultiplekser 8 wytwarza osiem wyjść. Aby uzyskać ostateczny wynik, potrzebujemy 1 × 2 demultiplekser do wytwarzania dwóch wyjść z jednego wejścia. Następnie przekazujemy te wyjścia do obu demultiplekserów jako dane wejściowe. Schemat blokowy 1 × 16 demultipleksera wykorzystującego 1 × 8 i 1 × 2 de-multiplekser podano poniżej.