Verilog-zaakverklaring

Verilog Case Statement met wat is Verilog, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog Case Statement met wat is Verilog, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog-tutorial met wat is Verilog, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog-parameters met wat is Verilog, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog blokkeert altijd met wat Verilog is, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog Assign-verklaring met wat Verilog is, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

Verilog-operators met wat Verilog is, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.

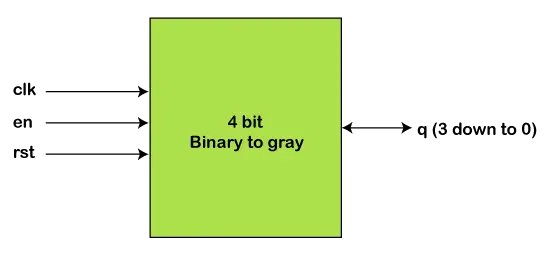

Verilog Gray Counter met wat is Verilog, lexicale tokens, ASIC Design Flow, chip-abstractielagen, Verilog-gegevenstypen, Verilog-module, RTL Verilog, arrays, poort enz.