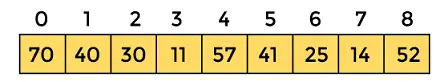

De-multiplexer

Een de-multiplexer is een combinatiecircuit dat slechts 1 ingangslijn en 2 ingangslijnen heeft N uitvoerlijnen. Simpel gezegd is de multiplexer een combinatiecircuit met één ingang en meerdere uitgangen. De informatie wordt ontvangen van de enkele invoerlijnen en naar de uitvoerlijn geleid. Op basis van de waarden van de selectieregels wordt de ingang aangesloten op één van deze uitgangen. De-multiplexer is het tegenovergestelde van de multiplexer.

In tegenstelling tot encoder en decoder zijn er n selectieregels en 2 N uitgangen. Er zijn er dus in totaal 2 N mogelijke combinaties van ingangen. De-multiplexer wordt ook behandeld als De-mux .

Er zijn verschillende soorten de-multiplexers:

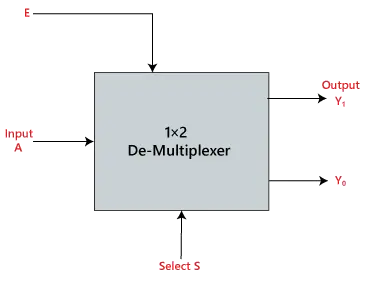

1×2 de-multiplexer:

In de 1 tot 2 de-multiplexer zijn er slechts twee uitgangen, namelijk Y 0 , en Y 1 , 1 selectielijnen, d.w.z. S 0 en enkele ingang, d.w.z. A. Op basis van de selectiewaarde wordt de ingang verbonden met een van de uitgangen. Het blokdiagram en de waarheidstabel van de 1 × Hieronder worden 2 multiplexers gegeven.

Blokdiagram:

Waarheidstabel:

De logische uitdrukking van de term Y is als volgt:

EN 0 =S 0 '.A

EN 1 =S 0 .A

Logisch circuit van de bovenstaande uitdrukkingen wordt hieronder gegeven:

1×4 de-multiplexer:

In de 1 tot 4 de-multiplexer zijn er in totaal vier uitgangen, d.w.z. Y 0 , EN 1 , EN 2 , en Y 3 , 2 selectielijnen, d.w.z. S 0 en S 1 en enkele ingang, d.w.z. A. Op basis van de combinatie van ingangen die aanwezig zijn op de selectielijnen S 0 en S 1 , moet de ingang worden aangesloten op een van de uitgangen. Het blokdiagram en de waarheidstabel van de 1 × 4 multiplexers worden hieronder gegeven.

Blokdiagram:

Waarheidstabel:

De logische uitdrukking van de term Y is als volgt:

EN 0 =S 1 ' S 0 ' A

En 1 =S 1 ' S 0 A

En 2 =S 1 S 0 ' A

En 3 =S 1 S 0 A

Logisch circuit van de bovenstaande uitdrukkingen wordt hieronder gegeven:

1×8 De-multiplexer

In de 1 tot 8 de-multiplexer zijn er in totaal acht uitgangen, d.w.z. Y 0 , EN 1 , EN 2 , EN 3 , EN 4 , EN 5 , EN 6 , en Y 7 , 3 selectielijnen, d.w.z. S 0 , S 1 en S 2 en enkele ingang, d.w.z. A. Op basis van de combinatie van ingangen die aanwezig zijn op de selectielijnen S 0 , S 1 en S 2 , wordt de ingang aangesloten op een van deze uitgangen. Het blokdiagram en de waarheidstabel van de 1 × 8 de-multiplexer worden hieronder gegeven.

Blokdiagram:

Waarheidstabel:

De logische uitdrukking van de term Y is als volgt:

EN 0 =S 0 '.S 1 '.S 2 '.A

EN 1 =S 0 .S 1 '.S 2 '.A

EN 2 =S 0 '.S 1 .S 2 '.A

EN 3 =S 0 .S 1 .S 2 '.A

EN 4 =S 0 '.S 1 '.S 2 A

EN 5 =S 0 .S 1 '.S 2 A

EN 6 =S 0 '.S 1 .S 2 A

EN 7 =S 0 .S 1 .S 3 .A

Logisch circuit van de bovenstaande uitdrukkingen wordt hieronder gegeven:

1×8 de-multiplexer met behulp van 1×4 en 1×2 de-multiplexer

Wij kunnen de 1 × 8 de-multiplexer met behulp van een de-multiplexer van lagere orde. Het implementeren van de 1 × 8 de-multiplexer, we hebben er twee nodig 1 × 4 de-multiplexer en één 1 × 2 de-multiplexer. De 1 × 4 multiplexer heeft 2 selectielijnen, 4 uitgangen en 1 ingang. De 1 × 2 de-multiplexer heeft slechts 1 selectielijn.

Om 8 data-uitgangen te krijgen, hebben we twee 1 × 4 de-multiplexer. De 1×2 de-multiplexer produceert twee uitgangen. Om de uiteindelijke uitvoer te krijgen, moeten we dus de uitvoer van de 1×2 de-multiplexer doorgeven als invoer van zowel de 1 × 4 de-multiplexer. Het blokschema van 1 × 8 de-multiplexer met 1 × 4 en 1 × 2 de-multiplexer wordt hieronder gegeven.

1 x 16 de-multiplexer

In een 1×16 de-multiplexer zijn er in totaal 16 uitgangen, d.w.z. Y 0 , EN 1 , …, EN 16 , 4 selectielijnen, d.w.z. S 0 , S 1 , S 2 , en S 3 en enkele ingang, d.w.z. A. Op basis van de combinatie van ingangen die aanwezig zijn op de selectielijnen S 0 , S 1 , en S 2 , wordt de ingang aangesloten op een van deze uitgangen. Het blokdiagram en de waarheidstabel van de 1 × 16 de-multiplexer worden hieronder gegeven.

Blokdiagram:

Waarheidstabel:

De logische uitdrukking van de term Y is als volgt:

EN 0 =AS 0 '.S 1 '.S 2 '.S 3 '

EN 1 =AS 0 '.S 1 '.S 2 '.S 3

EN 2 =AS 0 '.S 1 '.S 2 .S 3 '

EN 3 =AS 0 '.S 1 '.S 2 .S 3

EN 4 =AS 0 '.S 1 .S 2 '.S 3 '

EN 5 =AS 0 '.S 1 .S 2 '.S 3

EN 6 =AS 0 '.S 1 .S 2 .S 3 '

EN 7 =AS 0 '.S 1 .S 2 .S 3

EN 8 =AS 0 .S 1 '.S 2 '.S 3 '

EN 9 =AS 0 .S 1 '.S 2 '.S 3

EN 10 =AS 0 .S 1 '.S 2 .S 3 '

EN elf =AS 0 .S 1 '.S 2 .S 3

EN 12 =AS 0 .S 1 .S 2 '.S 3 '

EN 13 =AS 0 .S 1 .S 2 '.S 3

EN 14 =AS 0 .S 1 .S 2 .S 3 '

EN vijftien =AS 0 .S 1 .S 2 '.S 3

Logisch circuit van de bovenstaande uitdrukkingen wordt hieronder gegeven:

1×16 de-multiplexer met behulp van 1×8 en 1×2 de-multiplexer

Wij kunnen de 1 × 16 de-multiplexer met behulp van een de-multiplexer van lagere orde. Het implementeren van de 1 × 16 de-multiplexer, we hebben er twee nodig 1 × 8 de-multiplexer en één 1 × 2 de-multiplexer. De 1 × 8 multiplexer heeft 3 selectielijnen, 1 ingang en 8 uitgangen. De 1 × 2 de-multiplexer heeft slechts 1 selectielijn.

Om 16 data-uitgangen te krijgen, hebben we twee 1×8 de-multiplexers nodig. De 1 × 8 de-multiplexer produceert acht uitgangen. Om de uiteindelijke uitvoer te krijgen, hebben we dus een 1 nodig × 2 de-multiplexer om twee uitgangen te produceren vanuit één enkele ingang. Vervolgens geven we deze uitgangen door aan zowel de de-multiplexer als een ingang. Het blokschema van 1 × 16 de-multiplexer met 1 × 8 en 1 × 2 de-multiplexer wordt hieronder gegeven.