Demultiplexer

Un demultiplexer è un circuito combinatorio che ha solo 1 linea di ingresso e 2 N linee di uscita. Semplicemente, il multiplexer è un circuito combinatorio a ingresso singolo e multi-uscita. Le informazioni vengono ricevute dalle singole linee di ingresso e dirette alla linea di uscita. In base ai valori delle righe di selezione l'ingresso verrà collegato ad una di queste uscite. Il demultiplexer è l'opposto del multiplexer.

A differenza di encoder e decoder, ci sono n linee di selezione e 2 N uscite. Quindi in totale sono 2 N possibili combinazioni di input. Anche il demultiplexer viene trattato come Demux .

Esistono vari tipi di demultiplexer che sono i seguenti:

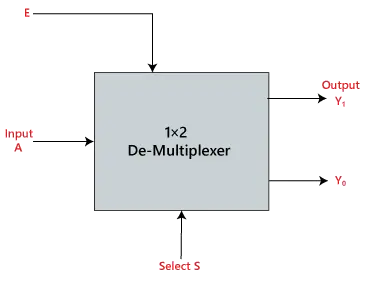

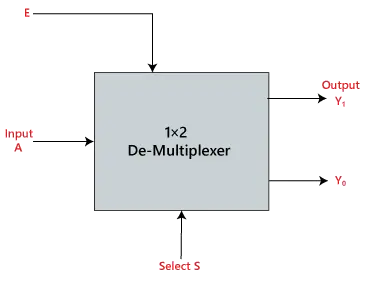

Demultiplexer 1×2:

Nel demultiplexer 1 a 2 ci sono solo due uscite, cioè Y 0 , e Y 1 , 1 riga di selezione, ovvero S 0 , e ingresso singolo, cioè A. In base al valore selezionato, l'ingresso verrà collegato ad una delle uscite. Lo schema a blocchi e la tavola di verità della 1 × Di seguito sono riportati 2 multiplexer.

Diagramma a blocchi:

Tabella della verità:

L’espressione logica del termine Y è la seguente:

E 0 =S 0 '.UN

E 1 =S 0 .UN

Il circuito logico delle espressioni di cui sopra è riportato di seguito:

Demultiplexer 1×4:

Nel demultiplexer da 1 a 4 sono presenti in totale quattro uscite, ovvero Y 0 , E 1 , E 2 , e Y 3 , 2 linee di selezione, cioè S 0 e S 1 e ingresso singolo, cioè A. In base alla combinazione degli ingressi presenti sulle linee di selezione S 0 e S 1 , l'ingresso deve essere collegato a una delle uscite. Lo schema a blocchi e la tavola di verità della 1 × Di seguito sono riportati 4 multiplexer.

Diagramma a blocchi:

Tabella della verità:

L’espressione logica del termine Y è la seguente:

E 0 =S 1 ' S 0 ' UN

E 1 =S 1 ' S 0 UN

E 2 =S 1 S 0 ' UN

E 3 =S 1 S 0 UN

Il circuito logico delle espressioni di cui sopra è riportato di seguito:

Demultiplexer 1×8

Nel demultiplexer da 1 a 8 sono presenti in totale otto uscite, ovvero Y 0 , E 1 , E 2 , E 3 , E 4 , E 5 , E 6 , e Y 7 , 3 linee di selezione, cioè S 0 , S 1 e S 2 e ingresso singolo, cioè A. In base alla combinazione degli ingressi presenti sulle linee di selezione S 0 , S 1 e S 2 , l'ingresso sarà collegato a una di queste uscite. Lo schema a blocchi e la tavola di verità della 1 × Di seguito sono riportati 8 demultiplexer.

Diagramma a blocchi:

Tabella della verità:

L’espressione logica del termine Y è la seguente:

E 0 =S 0 '.S 1 '.S 2 '.UN

E 1 =S 0 .S 1 '.S 2 '.UN

E 2 =S 0 '.S 1 .S 2 '.UN

E 3 =S 0 .S 1 .S 2 '.UN

E 4 =S 0 '.S 1 '.S 2 UN

E 5 =S 0 .S 1 '.S 2 UN

E 6 =S 0 '.S 1 .S 2 UN

E 7 =S 0 .S 1 .S 3 .UN

Il circuito logico delle espressioni di cui sopra è riportato di seguito:

Demultiplexer 1×8 che utilizza demultiplexer 1×4 e 1×2

Possiamo implementare il 1 × 8 demultiplexer che utilizza un demultiplexer di ordine inferiore. Per implementare il 1 × 8 demultiplexer, ne servono due 1 × 4 demultiplexer e uno 1 × 2 demultiplexer. L'1 × Il multiplexer 4 ha 2 linee di selezione, 4 uscite e 1 ingresso. L'1 × 2 demultiplexer hanno solo 1 linea di selezione.

Per ottenere 8 output di dati, abbiamo bisogno di due 1 × 4 demultiplexer. Il demultiplexer 1×2 produce due uscite. Quindi, per ottenere l'output finale, dobbiamo passare le uscite del demultiplexer 1×2 come input di entrambi i 1 × 4 demultiplexer. Lo schema a blocchi di 1 × 8 demultiplexer utilizzando 1 × 4 e 1 × 2 de-multiplexer è riportato di seguito.

1 demultiplatore x 16

Nel demultiplexer 1×16, ci sono un totale di 16 uscite, cioè Y 0 , E 1 , …, E 16 , 4 righe di selezione, ovvero S 0 , S 1 , S 2 , e S 3 e ingresso singolo, cioè A. In base alla combinazione degli ingressi presenti sulle linee di selezione S 0 , S 1 , e S 2 , l'ingresso sarà collegato a una di queste uscite. Lo schema a blocchi e la tavola di verità della 1 × Di seguito sono riportati 16 demultiplexer.

Diagramma a blocchi:

Tabella della verità:

L’espressione logica del termine Y è la seguente:

E 0 =A.S 0 '.S 1 '.S 2 '.S 3 '

E 1 =A.S 0 '.S 1 '.S 2 '.S 3

E 2 =A.S 0 '.S 1 '.S 2 .S 3 '

E 3 =A.S 0 '.S 1 '.S 2 .S 3

E 4 =A.S 0 '.S 1 .S 2 '.S 3 '

E 5 =A.S 0 '.S 1 .S 2 '.S 3

E 6 =A.S 0 '.S 1 .S 2 .S 3 '

E 7 =A.S 0 '.S 1 .S 2 .S 3

E 8 =A.S 0 .S 1 '.S 2 '.S 3 '

E 9 =A.S 0 .S 1 '.S 2 '.S 3

E 10 =A.S 0 .S 1 '.S 2 .S 3 '

E undici =A.S 0 .S 1 '.S 2 .S 3

E 12 =A.S 0 .S 1 .S 2 '.S 3 '

E 13 =A.S 0 .S 1 .S 2 '.S 3

E 14 =A.S 0 .S 1 .S 2 .S 3 '

E quindici =A.S 0 .S 1 .S 2 '.S 3

Il circuito logico delle espressioni di cui sopra è riportato di seguito:

Demultiplexer 1×16 che utilizza demultiplexer 1×8 e 1×2

Possiamo implementare il 1 × 16 demultiplexer che utilizza un demultiplexer di ordine inferiore. Per implementare il 1 × 16 demultiplexer, ne servono due 1 × 8 demultiplexer e uno 1 × 2 demultiplexer. L'1 × Il multiplexer 8 ha 3 linee di selezione, 1 ingresso e 8 uscite. L'1 × 2 demultiplexer hanno solo 1 linea di selezione.

Per ottenere 16 uscite dati, abbiamo bisogno di due demultiplexer 1×8. L'1 × 8 demultiplexer producono otto uscite. Quindi, per ottenere l'output finale, abbiamo bisogno di 1 × 2 demultiplexer per produrre due uscite da un unico ingresso. Quindi passiamo queste uscite sia al demultiplexer che all'ingresso. Lo schema a blocchi di 1 × 16 demultiplexer utilizzando 1 × 8 e 1 × 2 de-multiplexer è riportato di seguito.