De-multiplexer

Un demultiplexor es un circuito combinacional que tiene solo 1 línea de entrada y 2 norte líneas de salida. Simplemente, el multiplexor es un circuito combinacional de una sola entrada y múltiples salidas. La información se recibe desde las líneas de entrada individuales y se dirige a la línea de salida. En base a los valores de las líneas de selección, la entrada se conectará a una de estas salidas. El demultiplexor es lo opuesto al multiplexor.

A diferencia del codificador y decodificador, hay n líneas de selección y 2 norte salidas. Entonces hay un total de 2 norte posibles combinaciones de entradas. El demultiplexor también se trata como De-mux .

Existen varios tipos de Demultiplexor que son los siguientes:

1×2 De-multiplexer:

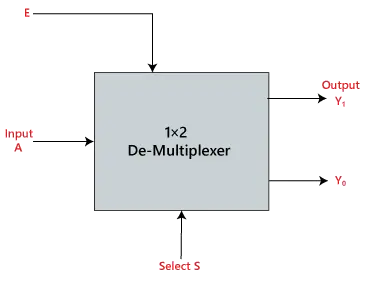

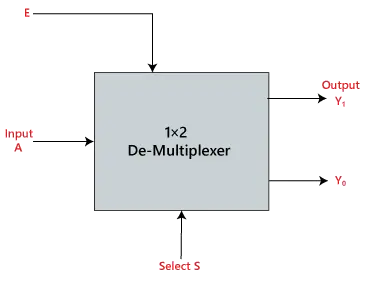

En el Demultiplexor 1 a 2, sólo hay dos salidas, es decir, Y 0 , y Y 1 , 1 líneas de selección, es decir, S 0 y entrada única, es decir, A. Según el valor seleccionado, la entrada se conectará a una de las salidas. El diagrama de bloques y la tabla de verdad del 1 × A continuación se muestran 2 multiplexores.

Diagrama de bloques:

Mesa de la verdad:

La expresión lógica del término Y es la siguiente:

Y 0 =S 0 '.A

Y 1 =S 0 .A

El circuito lógico de las expresiones anteriores se proporciona a continuación:

1×4 De-multiplexer:

En los demultiplexores 1 a 4, hay un total de cuatro salidas, es decir, Y 0 , Y 1 , Y 2 , y Y 3 , 2 líneas de selección, es decir, S 0 y S 1 y entrada única, es decir, A. Sobre la base de la combinación de entradas que están presentes en las líneas de selección S 0 y S 1 , la entrada se conectará a una de las salidas. El diagrama de bloques y la tabla de verdad del 1 × A continuación se detallan 4 multiplexores.

Diagrama de bloques:

Mesa de la verdad:

La expresión lógica del término Y es la siguiente:

Y 0 =S 1 ' S 0 ' A

y 1 =S 1 ' S 0 A

y 2 =S 1 S 0 ' A

y 3 =S 1 S 0 A

El circuito lógico de las expresiones anteriores se proporciona a continuación:

1×8 De-multiplexer

En los demultiplexores 1 a 8, hay un total de ocho salidas, es decir, Y 0 , Y 1 , Y 2 , Y 3 , Y 4 , Y 5 , Y 6 , y Y 7 , 3 líneas de selección, es decir, S 0 , S 1 y S 2 y entrada única, es decir, A. Sobre la base de la combinación de entradas que están presentes en las líneas de selección S 0 , S 1 y S 2 , la entrada se conectará a una de estas salidas. El diagrama de bloques y la tabla de verdad del 1 × A continuación se detallan 8 demultiplexores.

Diagrama de bloques:

Mesa de la verdad:

La expresión lógica del término Y es la siguiente:

Y 0 =S 0 '.S 1 '.S 2 '.A

Y 1 =S 0 .S 1 '.S 2 '.A

Y 2 =S 0 '.S 1 .S 2 '.A

Y 3 =S 0 .S 1 .S 2 '.A

Y 4 =S 0 '.S 1 '.S 2 A

Y 5 =S 0 .S 1 '.S 2 A

Y 6 =S 0 '.S 1 .S 2 A

Y 7 =S 0 .S 1 .S 3 .A

El circuito lógico de las expresiones anteriores se proporciona a continuación:

Demultiplexor 1×8 usando demultiplexor 1×4 y 1×2

Podemos implementar el 1 × 8 demultiplexor utilizando un demultiplexor de orden inferior. Para implementar el 1 × 8 demultiplexor, necesitamos dos 1 × 4 demultiplexores y uno 1 × 2 demultiplexores. el 1 × 4 multiplexores tienen 2 líneas de selección, 4 salidas y 1 entrada. el 1 × 2 demultiplexores tienen solo 1 línea de selección.

Para obtener 8 salidas de datos, necesitamos dos 1 × 4 demultiplexores. El demultiplexor 1×2 produce dos salidas. Entonces, para obtener la salida final, tenemos que pasar las salidas del demultiplexor 1×2 como entrada tanto del 1 × 4 demultiplexores. El diagrama de bloques de 1 × 8 demultiplexores usando 1 × 4 y 1 × A continuación se detallan 2 demultiplexores.

1 x 16 De-multiplexer

En un demultiplexor 1×16, hay un total de 16 salidas, es decir, Y 0 , Y 1 , …, Y 16 , 4 líneas de selección, es decir, S 0 , S 1 , S 2 y S 3 y entrada única, es decir, A. Sobre la base de la combinación de entradas que están presentes en las líneas de selección S 0 , S 1 y S 2 , la entrada se conectará a una de estas salidas. El diagrama de bloques y la tabla de verdad del 1 × A continuación se muestran 16 demultiplexores.

Diagrama de bloques:

Mesa de la verdad:

La expresión lógica del término Y es la siguiente:

Y 0 =A.S 0 '.S 1 '.S 2 '.S 3 '

Y 1 =A.S 0 '.S 1 '.S 2 '.S 3

Y 2 =A.S 0 '.S 1 '.S 2 .S 3 '

Y 3 =A.S 0 '.S 1 '.S 2 .S 3

Y 4 =A.S 0 '.S 1 .S 2 '.S 3 '

Y 5 =A.S 0 '.S 1 .S 2 '.S 3

Y 6 =A.S 0 '.S 1 .S 2 .S 3 '

Y 7 =A.S 0 '.S 1 .S 2 .S 3

Y 8 =A.S 0 .S 1 '.S 2 '.S 3 '

Y 9 =A.S 0 .S 1 '.S 2 '.S 3

Y 10 =A.S 0 .S 1 '.S 2 .S 3 '

Y 11 =A.S 0 .S 1 '.S 2 .S 3

Y 12 =A.S 0 .S 1 .S 2 '.S 3 '

Y 13 =A.S 0 .S 1 .S 2 '.S 3

Y 14 =A.S 0 .S 1 .S 2 .S 3 '

Y 15 =A.S 0 .S 1 .S 2 '.S 3

El circuito lógico de las expresiones anteriores se proporciona a continuación:

Demultiplexor 1×16 usando demultiplexor 1×8 y 1×2

Podemos implementar el 1 × 16 demultiplexor usando un demultiplexor de orden inferior. Para implementar el 1 × 16 demultiplexor, necesitamos dos 1 × 8 demultiplexores y un 1 × 2 demultiplexores. el 1 × 8 multiplexor tiene 3 líneas de selección, 1 entrada y 8 salidas. el 1 × 2 demultiplexores tienen solo 1 línea de selección.

Para obtener 16 salidas de datos, necesitamos dos demultiplexores de 1×8. el 1 × 8 demultiplexor produce ocho salidas. Entonces, para obtener el resultado final, necesitamos un 1 × 2 demultiplexores para producir dos salidas desde una sola entrada. Luego pasamos estas salidas tanto al demultiplexor como a la entrada. El diagrama de bloques de 1 × 16 demultiplexor usando 1 × 8 y 1 × A continuación se detallan 2 demultiplexores.