Multiplexer

Multiplexer je kombinační obvod, který má 2 n vstupní linky a jeden výstupní řádek. Jednoduše řečeno, multiplexor je vícevstupový a jednovýstupový kombinační obvod. Binární informace jsou přijímány ze vstupních linek a směrovány do výstupní linky. Na základě hodnot výběrových řádků bude jeden z těchto datových vstupů připojen k výstupu.

Na rozdíl od kodéru a dekodéru existuje n výběrových řádků a 2 n vstupní řádky. Celkem jsou tedy 2 N možné kombinace vstupů. S multiplexerem se také zachází jako Mux .

Existují různé typy multiplexerů, které jsou následující:

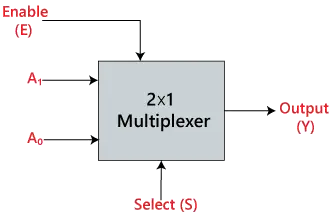

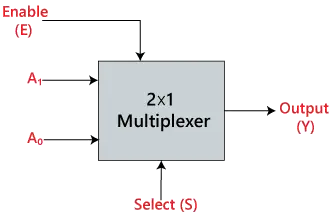

2×1 multiplexer:

V multiplexeru 2×1 jsou pouze dva vstupy, tedy A 0 a A 1 , 1 řádek výběru, tj. S 0 a jednotlivé výstupy, tj. Y. Na základě kombinace vstupů, které jsou na výběrové linii S 0 , jeden z těchto 2 vstupů bude připojen k výstupu. Blokové schéma a pravdivostní tabulka 2 × 1 multiplexer jsou uvedeny níže.

Blokové schéma:

Tabulka pravdy:

Logické vyjádření výrazu Y je následující:

Y=S 0 '.A 0 +S 0 .A 1

Logický obvod výše uvedeného výrazu je uveden níže:

4×1 multiplexer:

V multiplexeru 4×1 jsou celkem čtyři vstupy, tedy A 0 , A 1 , A 2 a A 3 , 2 výběrové řádky, tj. S 0 a S 1 a jeden výstup, tj. Y. Na základě kombinace vstupů, které jsou přítomné na výběrových liniích S 0 a S 1 , jeden z těchto 4 vstupů je připojen k výstupu. Blokové schéma a pravdivostní tabulka 4 × 1 multiplexer jsou uvedeny níže.

Blokové schéma:

Tabulka pravdy:

Logické vyjádření výrazu Y je následující:

Y=S 1 'S 0 'A 0 +S 1 'S 0 A 1 +S 1 S 0 'A 2 +S 1 S 0 A 3

Logický obvod výše uvedeného výrazu je uveden níže:

Multiplexer 8 na 1

V multiplexeru 8 na 1 je celkem osm vstupů, tedy A 0 , A 1 , A 2 , A 3 , A 4 , A 5 , A 6 a A 7 , 3 výběrové řádky, tj. S 0 , S 1 a S 2 a jeden výstup, tj. Y. Na základě kombinace vstupů, které jsou přítomné na výběrových řádcích S 0 , S 1, a S 2 , jeden z těchto 8 vstupů je připojen k výstupu. Blokové schéma a pravdivostní tabulka 8 × 1 multiplexer jsou uvedeny níže.

Blokové schéma:

Tabulka pravdy:

Logické vyjádření výrazu Y je následující:

Y=S 0 '.S 1 '.S 2 '.A 0 +S 0 .S 1 '.S 2 '.A 1 +S 0 '.S 1 .S 2 '.A 2 +S 0 .S 1 .S 2 '.A 3 +S 0 '.S 1 '.S 2 A 4 +S 0 .S 1 '.S 2 A 5 +S 0 '.S 1 .S 2 .A 6 +S 0 .S 1 .S 3 .A 7

Logický obvod výše uvedeného výrazu je uveden níže:

8 × 1 multiplexer využívající 4 × 1 a 2 × 1 multiplexer

Můžeme implementovat 8 × 1 multiplexer využívající multiplexor nižšího řádu. K realizaci 8 × 1 multiplexer, potřebujeme dva 4 × 1 multiplexer a jeden 2 × 1 multiplexer. 4 × 1 multiplexer má 2 výběrové řádky, 4 vstupy a 1 výstup. 2 × 1 multiplexer má pouze 1 řádek výběru.

Pro získání 8 datových vstupů potřebujeme dva 4 × 1 multiplexer. 4 × 1 multiplexer vytváří jeden výstup. Abychom získali konečný výstup, potřebujeme 2 × 1 multiplexer. Blokové schéma z 8 × 1 multiplexer pomocí 4 × 1 a 2 × 1 multiplexer je uveden níže.

16 na 1 multiplexer

V multiplexeru 16 na 1 je celkem 16 vstupů, tj. 0 , A 1 , …, A 16 , 4 výběrové řádky, tj. S 0 , S 1 , S 2 a S 3 a jeden výstup, tj. Y. Na základě kombinace vstupů, které jsou přítomné na výběrových řádcích S 0 , S 1 a S 2 , jeden z těchto 16 vstupů bude připojen k výstupu. Blokové schéma a pravdivostní tabulka 16 × 1

Blokové schéma:

Tabulka pravdy:

Logické vyjádření výrazu Y je následující:

Y=A 0 .S 0 '.S 1 '.S 2 '.S 3 '+A 1 .S 0 '.S 1 '.S 2 '.S 3 +A 2 .S 0 '.S 1 '.S 2 .S 3 '+A 3 .S 0 '.S 1 '.S 2 .S 3 +A 4 .S 0 '.S 1 .S 2 '.S 3 '+A 5 .S 0 '.S 1 .S 2 '.S 3 +A 6 .S 1 .S 2 .S 3 '+A 7 .S 0 '.S 1 .S 2 .S 3 +A 8 .S 0 .S 1 '.S 2 '.S 3 '+A 9 .S 0 .S 1 '.S 2 '.S 3 +Y 1 0.S 0 .S 1 '.S 2 .S 3 '+A 1 1.S 0 .S 1 '.S 2 .S 3 +A 1 2 S 0 .S 1 .S 2 '.S 3 '+A 1 3.S 0 .S 1 .S 2 '.S 3 +A 1 4.S 0 .S 1 .S 2 .S 3 '+A 1 5.S 0 .S 1 .S 2 '.S 3Logický obvod výše uvedeného výrazu je uveden níže:

16×1 multiplexer využívající 8×1 a 2×1 multiplexer

Můžeme implementovat 16 × 1 multiplexer využívající multiplexor nižšího řádu. K realizaci 8 × 1 multiplexer, potřebujeme dva 8 × 1 multiplexer a jeden 2 × 1 multiplexer. 8 × 1 multiplexor má 3 výběrové linky, 4 vstupy a 1 výstup. 2 × 1 multiplexer má pouze 1 řádek výběru.

Pro získání 16 datových vstupů potřebujeme dva multiplexery 8×1. 8 × 1 multiplexer vytváří jeden výstup. Takže, abychom získali konečný výstup, potřebujeme 2 × 1 multiplexer. Blokové schéma z 16 × 1 multiplexer pomocí 8 × 1 a 2 × 1 multiplexer je uveden níže.