Multiplexor

Un multiplexor és un circuit combinacional que té 2 n línies d'entrada i una única línia de sortida. Simplement, el multiplexor és un circuit combinat de múltiples entrades i sortida única. La informació binària es rep de les línies d'entrada i es dirigeix a la línia de sortida. A partir dels valors de les línies de selecció, una d'aquestes entrades de dades es connectarà a la sortida.

A diferència del codificador i el descodificador, hi ha n línies de selecció i 2 n línies d'entrada. Per tant, n'hi ha un total de 2 N possibles combinacions d'entrades. Un multiplexor també es tracta com Mux .

Hi ha diversos tipus de multiplexor que són els següents:

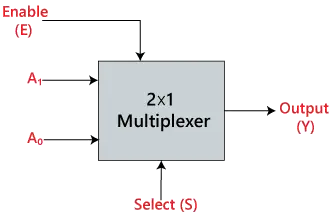

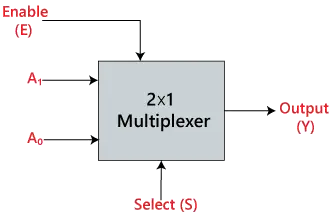

Multiplexor 2×1:

Al multiplexor 2×1, només hi ha dues entrades, és a dir, A 0 i A 1 , 1 línia de selecció, és a dir, S 0 i sortides individuals, és a dir, Y. Sobre la base de la combinació d'entrades que estan presents a la línia de selecció S 0 , una d'aquestes 2 entrades es connectarà a la sortida. El diagrama de blocs i la taula de veritat del 2 × A continuació es mostren 1 multiplexor.

Diagrama de blocs:

Taula de la veritat:

L'expressió lògica del terme Y és la següent:

I=S 0 '.A 0 +S 0 .A 1

El circuit lògic de l'expressió anterior es mostra a continuació:

Multiplexor 4×1:

Al multiplexor 4×1, hi ha un total de quatre entrades, és a dir, A 0 , A 1 , A 2 , i A 3 , 2 línies de selecció, és a dir, S 0 i S 1 i sortida única, és a dir, Y. Sobre la base de la combinació d'entrades que estan presents a les línies de selecció S 0 i S 1 , una d'aquestes 4 entrades està connectada a la sortida. El diagrama de blocs i la taula de veritat del 4 × A continuació es mostren 1 multiplexor.

Diagrama de blocs:

Taula de la veritat:

L'expressió lògica del terme Y és la següent:

I=S 1 'S 0 'A 0 +S 1 'S 0 A 1 +S 1 S 0 'A 2 +S 1 S 0 A 3

El circuit lògic de l'expressió anterior es mostra a continuació:

Multiplexor de 8 a 1

Al multiplexor 8 a 1, hi ha un total de vuit entrades, és a dir, A 0 , A 1 , A 2 , A 3 , A 4 , A 5 , A 6 , i A 7 , 3 línies de selecció, és a dir, S 0 , S 1 i S 2 i sortida única, és a dir, Y. Sobre la base de la combinació d'entrades que estan presents a les línies de selecció S 0 , S 1, i S 2 , una d'aquestes 8 entrades està connectada a la sortida. El diagrama de blocs i la taula de veritat del 8 × A continuació es mostren 1 multiplexor.

Diagrama de blocs:

Taula de la veritat:

L'expressió lògica del terme Y és la següent:

I=S 0 '.S 1 '.S 2 '.A 0 +S 0 .S 1 '.S 2 '.A 1 +S 0 '.S 1 .S 2 '.A 2 +S 0 .S 1 .S 2 '.A 3 +S 0 '.S 1 '.S 2 A 4 +S 0 .S 1 '.S 2 A 5 +S 0 '.S 1 .S 2 .A 6 +S 0 .S 1 .S 3 .A 7

El circuit lògic de l'expressió anterior es mostra a continuació:

Multiplexor 8 × 1 amb multiplexor 4 × 1 i 2 × 1

Podem implementar el 8 × 1 multiplexor utilitzant un multiplexor d'ordre inferior. Per implementar el 8 × 1 multiplexor, necessitem dos 4 × 1 multiplexor i un 2 × 1 multiplexor. El 4 × 1 multiplexor té 2 línies de selecció, 4 entrades i 1 sortida. El 2 × 1 multiplexor només té 1 línia de selecció.

Per obtenir 8 entrades de dades, necessitem dues 4 × 1 multiplexor. El 4 × 1 multiplexor produeix una sortida. Per tant, per obtenir la sortida final, necessitem un 2 × 1 multiplexor. El diagrama de blocs de 8 × 1 multiplexor amb 4 × 1 i 2 × A continuació es mostra 1 multiplexor.

Multiplexor de 16 a 1

Al multiplexor 16 a 1, hi ha un total de 16 entrades, és a dir, A 0 , A 1 ,…, A 16 , 4 línies de selecció, és a dir, S 0 , S 1 , S 2 , i S 3 i sortida única, és a dir, Y. Sobre la base de la combinació d'entrades que estan presents a les línies de selecció S 0 , S 1 , i S 2 , una d'aquestes 16 entrades es connectarà a la sortida. El diagrama de blocs i la taula de veritat del 16 × 1

Diagrama de blocs:

Taula de la veritat:

L'expressió lògica del terme Y és la següent:

I=A 0 .S 0 '.S 1 '.S 2 '.S 3 '+A 1 .S 0 '.S 1 '.S 2 '.S 3 +A 2 .S 0 '.S 1 '.S 2 .S 3 '+A 3 .S 0 '.S 1 '.S 2 .S 3 +A 4 .S 0 '.S 1 .S 2 '.S 3 '+A 5 .S 0 '.S 1 .S 2 '.S 3 +A 6 .S 1 .S 2 .S 3 '+A 7 .S 0 '.S 1 .S 2 .S 3 +A 8 .S 0 .S 1 '.S 2 '.S 3 '+A 9 .S 0 .S 1 '.S 2 '.S 3 +I 1 0.S 0 .S 1 '.S 2 .S 3 '+A 1 1.S 0 .S 1 '.S 2 .S 3 +A 1 2 S 0 .S 1 .S 2 '.S 3 '+A 1 3.S 0 .S 1 .S 2 '.S 3 +A 1 4.S 0 .S 1 .S 2 .S 3 '+A 1 5.S 0 .S 1 .S 2 '.S 3El circuit lògic de l'expressió anterior es mostra a continuació:

Multiplexor 16×1 amb multiplexor 8×1 i 2×1

Podem implementar el 16 × 1 multiplexor utilitzant un multiplexor d'ordre inferior. Per implementar el 8 × 1 multiplexor, necessitem dos 8 × 1 multiplexor i un 2 × 1 multiplexor. El 8 × 1 multiplexor té 3 línies de selecció, 4 entrades i 1 sortida. El 2 × 1 multiplexor només té 1 línia de selecció.

Per obtenir 16 entrades de dades, necessitem dos multiplexors de 8 × 1. El 8 × 1 multiplexor produeix una sortida. Per tant, per obtenir la sortida final, necessitem un 2 × 1 multiplexor. El diagrama de blocs de 16 × 1 multiplexor amb 8 × 1 i 2 × A continuació es mostra 1 multiplexor.